2025-10-29 03:11:12

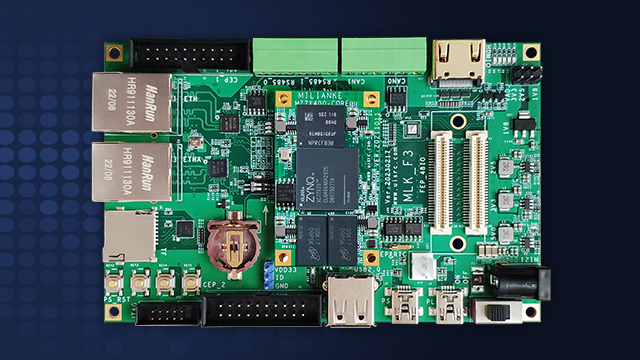

FPGA開發(fā)板是電子工程師與愛好者探索硬件世界的重要載體,其硬件架構(gòu)設計精巧且功能豐富。以常見的XilinxZynq系列開發(fā)板為例,這類開發(fā)板集成了ARM處理器與FPGA可編程邏輯資源,形成獨特的異構(gòu)架構(gòu)。ARM處理器部分可運行嵌入式操作系統(tǒng),用于處理復雜的系統(tǒng)管理任務和軟件算法,諸如文件系統(tǒng)管理、網(wǎng)絡通信協(xié)議棧運行等;而FPGA部分則可根據(jù)設計需求靈活構(gòu)建各類數(shù)字電路。開發(fā)板上還配備了豐富的存儲模塊,包括用于程序存儲的Flash芯片,能在斷電后長久保存系統(tǒng)啟動代碼與用戶程序;以及用于數(shù)據(jù)緩存的DDR內(nèi)存,可在運行時存取大量數(shù)據(jù)。此外,開發(fā)板設置多種通信接口,以太網(wǎng)接口方便連接網(wǎng)絡進行數(shù)據(jù)傳輸與遠程調(diào)試,USB接口支持多種設備連接,方便數(shù)據(jù)交互,SPI、I?C等接口則用于連接各類傳感器與外設芯片,為開發(fā)者搭建復雜硬件系統(tǒng)提供了充足的拓展空間。FPGA 開發(fā)板用戶指南含常見問題解答。XilinxFPGA開發(fā)板交流

FPGA開發(fā)板的功耗分為靜態(tài)功耗和動態(tài)功耗,靜態(tài)功耗是芯片未工作時的漏電流功耗,動態(tài)功耗是芯片工作時邏輯切換和信號傳輸產(chǎn)生的功耗,選型和設計時需根據(jù)應用場景優(yōu)化功耗。低功耗FPGA開發(fā)板通常采用40nm、28nm等先進工藝芯片,集成功耗管理模塊,支持動態(tài)電壓頻率調(diào)節(jié)(DVFS),可根據(jù)工作負載調(diào)整電壓和頻率,降低空閑時的功耗,適合便攜設備、物聯(lián)網(wǎng)節(jié)點等電池供電場景。例如XilinxZynqUltraScale+MPSoC系列芯片,支持多種功耗模式,靜態(tài)功耗可低至幾十毫瓦。高功耗開發(fā)板則注重性能,采用16nm、7nm工藝芯片,支持高速接口和大量并行計算,適合固定設備、數(shù)據(jù)中心等有穩(wěn)定電源供應的場景。功耗優(yōu)化還可通過設計層面實現(xiàn),如減少不必要的邏輯切換、優(yōu)化時鐘網(wǎng)絡、使用低功耗IP核等。在實際應用中,需平衡功耗與性能,例如邊緣計算場景需優(yōu)先考慮低功耗,而數(shù)據(jù)中心加速場景需優(yōu)先考慮性能。 重慶工控板FPGA開發(fā)板學習步驟FPGA 開發(fā)板接口間距符合標準封裝尺寸。

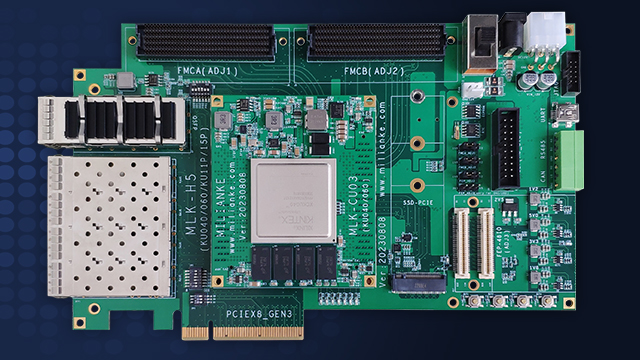

FPGA開發(fā)板的信號完整性是指信號在傳輸過程中保持原有特性的能力,直接影響系統(tǒng)的穩(wěn)定性和性能,尤其在高速接口(如PCIe、DDR、HDMI)設計中至關重要。信號完整性優(yōu)化需從PCB設計、元器件選型和時序約束三個方面入手。PCB設計中,需控制傳輸線阻抗匹配(如50Ω、100Ω差分),避免阻抗突變導致信號反射;采用差分信號傳輸,減少電磁干擾(EMI);優(yōu)化布線拓撲,縮短信號路徑,減少串擾。元器件選型中,需選用高速率、低抖動的晶體振蕩器和時鐘緩沖器,確保時鐘信號穩(wěn)定;選用低寄生參數(shù)的連接器和電容電阻,減少信號衰減。時序約束中,需在開發(fā)工具中設置合理的時鐘周期、建立時間和保持時間,確保數(shù)據(jù)在正確的時序窗口內(nèi)傳輸;通過時序分析工具檢查時序違規(guī),調(diào)整邏輯布局和布線,實現(xiàn)時序收斂。信號完整性問題常表現(xiàn)為數(shù)據(jù)傳輸錯誤、圖像失真、接口不穩(wěn)定,可通過示波器觀察信號波形,分析反射、串擾、抖動等問題,針對性優(yōu)化設計。

FPGA開發(fā)板在物聯(lián)網(wǎng)領域的應用日益。在智能家居系統(tǒng)搭建中,開發(fā)板可作為樞紐連接各類智能設備。通過Wi-Fi或藍牙模塊,開發(fā)板與智能手機等終端設備建立通信,接收用戶的控制指令;同時,利用GPIO接口連接各類傳感器,如溫濕度傳感器、人體紅外傳感器等,實時采集家居環(huán)境數(shù)據(jù)。基于采集到的數(shù)據(jù),開發(fā)者可以在FPGA上編寫邏輯程序,實現(xiàn)自動化的家居控制場景。例如,當檢測到室內(nèi)溫度過高時,自動開啟空調(diào);檢測到有人進入房間,自動打開燈光。此外,開發(fā)板還可以通過以太網(wǎng)接口接入家庭網(wǎng)關,與云端服務器進行數(shù)據(jù)交互,實現(xiàn)遠程監(jiān)控與控制功能。用戶即便不在家中,也能通過手機APP查看家中設備狀態(tài),并進行遠程操作,為用戶打造便捷、智能的家居生活體驗。FPGA 開發(fā)板工業(yè)級型號適應復雜環(huán)境測試。

1FPGA開發(fā)板的電源電路設計FPGA開發(fā)板的電源電路是保障系統(tǒng)穩(wěn)定運行的基礎環(huán)節(jié),通常需提供多種電壓規(guī)格以適配不同組件需求。例如,F(xiàn)PGA芯片可能需要1.2V或1.8V低壓供電,而外圍接口如USB、HDMI則需5V或3.3V電壓。這類電路會集成線性穩(wěn)壓器或開關電源模塊,前者優(yōu)勢在于輸出紋波小,適合對供電精度要求高的場景,后者則具備更高的轉(zhuǎn)換效率,能應對FPGA高負載運行時的功耗波動。部分開發(fā)板還會加入電源指示燈和過流保護電路,前者方便開發(fā)者直觀判斷供電狀態(tài),后者可避免因外接設備故障導致的板卡損壞,尤其在多模塊擴展實驗中,穩(wěn)定的電源供給能減少因電壓波動引發(fā)的邏輯功能異常。FPGA 開發(fā)板硬件資源配置可軟件查詢。山東安路開發(fā)板FPGA開發(fā)板入門

FPGA 開發(fā)板讓理論知識轉(zhuǎn)化為實踐能力!XilinxFPGA開發(fā)板交流

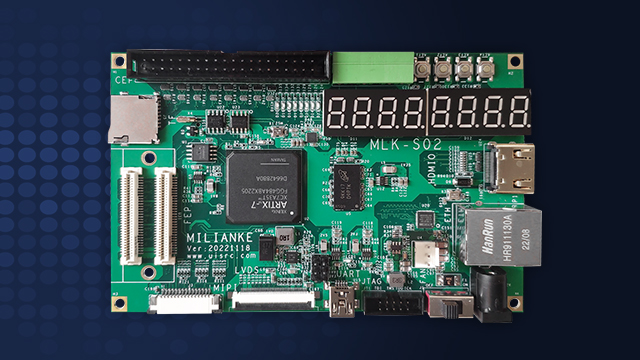

FPGA芯片的邏輯資源是衡量開發(fā)板性能的重要指標,包括邏輯單元(LE)、查找表(LUT)、觸發(fā)器(FF)、DSP切片和塊RAM(BRAM)等,選型時需根據(jù)項目需求匹配資源規(guī)模。對于入門級項目,如基礎邏輯實驗、簡單控制器設計,選擇邏輯單元數(shù)量在1萬-10萬之間的FPGA芯片即可,如XilinxArtix-7系列的xc7a35t芯片,具備35k邏輯單元、50個DSP切片和900KBBRAM,能滿足基礎開發(fā)需求。對于要求高的項目,如AI推理加速、高速數(shù)據(jù)處理,需選擇邏輯單元數(shù)量在10萬-100萬之間的芯片,如XilinxKintex-7系列的xc7k325t芯片,具備326k邏輯單元、1728個DSP切片和BRAM,支持復雜算法的實現(xiàn)。DSP切片數(shù)量影響信號處理能力,適合需要大量乘法累加運算的場景;塊RAM容量影響數(shù)據(jù)緩存能力,適合需要存儲大量中間數(shù)據(jù)的項目。選型時需避免資源過剩導致成本浪費,也需防止資源不足無法實現(xiàn)設計功能,可通過前期需求分析和資源估算確定合適的芯片型號。 XilinxFPGA開發(fā)板交流